## Transformations in High-Level Synthesis: Formal Specification and Efficient Mechanical Verification

P. Sreeranga Rajan Computer Science Laboratory SRI International Menlo Park CA 94025 USA

sree@csl.sri.com Phone: +1 (415) 859-2873 Fax: +1 (415) 859-2844

> Technical Report CSL-94-10 October 1994

#### Abstract

Dependency graphs are used to model data and control flow in hardware and software design. In high-level synthesis of hardware, optimization and refinement transformations are used to transform dependency-graph-based specifications at the behavior level to dependency-graph-based implementations at the register-transfer level. Registertransfer-level implementations are mapped to gate-level hardware designs by low-level logic synthesis. In this work, we investigated the specification and mechanical verification of the correctness of transformations used in high-level synthesis of hardware.

We have provided a formal specification of dependency graphs, and verified the correctness of a variety of transformations used in an industrial synthesis framework. Errors have been discovered in the transformations, and modifications have been proposed and incorporated. Further, the formal specification has permitted us to examine the generalization and composition of transformations. In the process, we have discovered new transformations that could be used for further optimization and refinement than were possible before. The specification and verification schemes are general enough for applications in other synthesis frameworks and software design, where a transformational design approach is used.

In order to present our work in a concrete context, we focus on the high-level synthesis part of the SPRITE project at Philips Research Laboratories. The transformations in the high-level synthesis system are used for refinement and optimization of descriptions specified in a dependency graph language called the SPRITE Input Language (SIL). SIL is an intermediate language used during the synthesis of hardware described using languages such as VHDL, SILAGE and ELLA. Besides being an intermediate language, it forms the backbone of the TRADES synthesis system of the University of Twente. SIL has been used in the design of hardware for audio and video applications.

We used the Prototype Verification System (PVS) from SRI International to specify and mechanically verify the correctness of the transformations. The PVS specification language allows us to investigate the correctness problem using a convenient level of representation. The PVS verifier features automatic procedures and interactive verification rules to check properties of specifications.

# Contents

|          | Ack  | nowledgments                                    | vi        |

|----------|------|-------------------------------------------------|-----------|

| 1        | Intr | oduction                                        | 1         |

|          | 1.1  | Related Work                                    | 6         |

|          |      | 1.1.1 LAMBDA                                    | 7         |

|          |      | 1.1.2 Formal Ruby                               | 7         |

|          |      | 1.1.3 Digital Design Derivation                 | 8         |

|          |      | 1.1.4 Transformations in SAW                    | 8         |

|          |      | 1.1.5 Verification of Transformations in SILAGE | 8         |

|          |      | 1.1.6 Synchronized Transitions in LP            | 8         |

|          |      | 1.1.7 Transformations in Software Design        | 9         |

| <b>2</b> | Ove  | rview of SIL                                    | 11        |

|          | 2.1  | Structural Aspects of SIL                       | 11        |

|          | 2.2  | Behavioral Aspects of SIL                       | 12        |

|          | 2.3  | Transformations in SIL                          | 18        |

| 3        | Spe  | ification and Verification in PVS               | <b>21</b> |

|          | 3.1  | PVS Specification Language                      | 21        |

|          | 3.2  | PVS Verification Features                       | 22        |

|          | 3.3  | Notes on Specification Notation                 | 22        |

|          | 3.4  | Specification and Verification Examples in PVS  | 24        |

| 4        | Spe  | ification of SIL Graph Structure in PVS         | 33        |

|          | 4.1  | Port and Port Array                             | 33        |

|          | 4.2  | Edges                                           | 34        |

|          | 4.3  | Node, Conditional Node and Graph                | 35        |

|          | 4.4  | Well-formedness of a SIL Graph                  | 39        |

| <b>5</b> | Spe                        | cification of SIL Graph Behavior and Refinement   | 41 |

|----------|----------------------------|---------------------------------------------------|----|

|          | 5.1                        | Behavior                                          | 41 |

|          | 5.2                        | Refinement and Equivalence                        | 42 |

| 6        | Spe                        | cification and Verification of Transformations    | 55 |

|          | 6.1                        | Overview                                          | 55 |

|          | 6.2                        | Common Subexpression Elimination                  | 56 |

|          | 6.3                        | Cross-Jumping Tail-Merging                        | 57 |

|          | 6.4                        | Other Transformations and Proofs                  | 60 |

|          | 6.5                        | Generalization and Composition of Transformations | 61 |

|          | 6.6                        | Investigations into "What-if?" Scenarios          | 61 |

|          | 6.7                        | Devising New Transformations                      | 62 |

| 7        | Discussion and Conclusions |                                                   |    |

|          | 7.1                        | Intent versus Implementation                      | 69 |

|          | 7.2                        | From Informal to Formal Specification             | 70 |

|          | 7.3                        | Axiomatic Approach versus Other Formal Approaches | 71 |

|          | 7.4                        | Conclusions and Future Work                       | 72 |

| A        | $\mathbf{Deff}$            | initions, Axioms and Theorems                     | 79 |

|          | A.1                        | Definitions                                       | 79 |

|          | A.2                        | Axioms                                            | 83 |

|          | A.3                        | Theorems                                          | 87 |

| в        | Pro                        | of Transcripts                                    | 95 |

|          | <b>B</b> .1                | Common Subexpression Elimination                  | 95 |

|          | B.2                        | Cross Jumping Tail Merging                        | 97 |

# List of Figures

| Cross jumping tail merging: incorrectly specified in informal document.                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example of a dependency graph with control specification                                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SIL transformations and verification in PVS in the context of high level synthesis.            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Different kinds of SIL ports                                                                   | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An example of a SIL graph description.                                                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

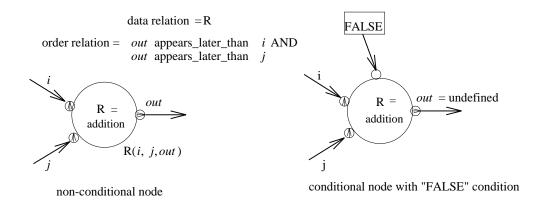

| SIL node: informal description                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

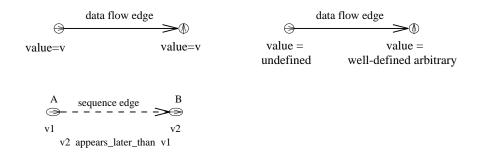

| SIL edges: informal description                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

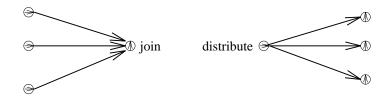

| SIL Join and Distribute: informal description                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

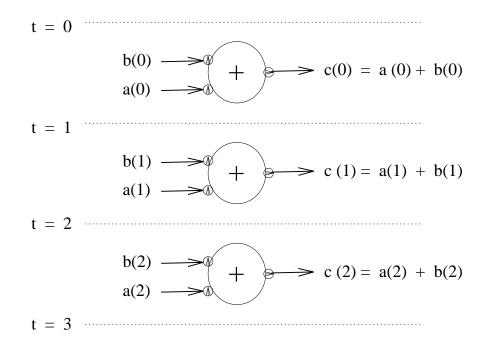

| Combinational adder: SIL graph repeated over clock cycles                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

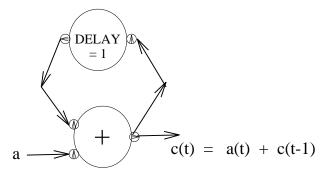

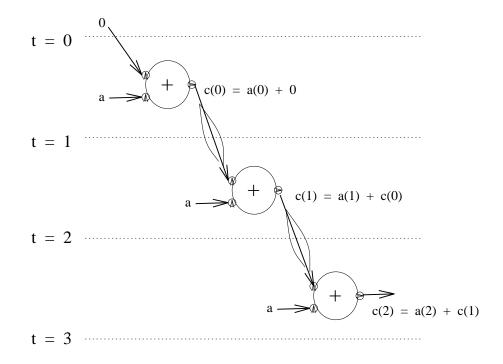

| Cumulative adder: SIL graph with DELAY node                                                    | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Cumulative adder: unfolded SIL graph                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Partial specification of a multiplexor                                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Implementation specification of a multiplexor                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example SIL transformation: retiming                                                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SIL data-flow and sequence edges.                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SIL conditional node                                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Node as a subtype of a conditional node                                                        | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example: refinement of ports due to non-deterministic choice                                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $Example: \ array \ refinement \ does \ not \ imply \ every \ individual \ port \ refinement.$ | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

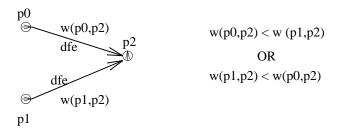

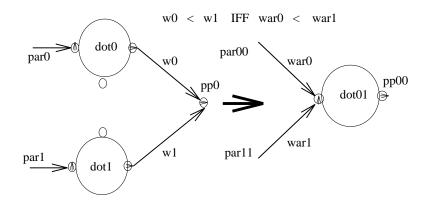

| Using weights for ordering data-flow edges                                                     | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Using weights to determine <i>join</i> behavior                                                | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

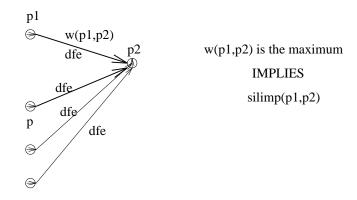

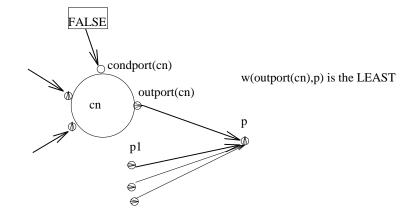

| Weight when the condition on a conditional node is false. $\ldots$                             | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Absence of <i>join</i> : exclusive data-flow edge                                              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                | Example of a dependency graph with control specification.SIL transformations and verification in PVS in the context of high level<br>synthesis.Different kinds of SIL ports.An example of a SIL graph description.SIL node: informal description.SIL edges: informal description.SIL of a mathematical description.SIL of a mathematical description.SIL on and Distribute: informal description.Combinational adder: SIL graph repeated over clock cycles.Cumulative adder: unfolded SIL graph.Partial specification of a multiplexor.Implementation specification of a multiplexor.SIL conditional node.SIL conditional node.Node as a subtype of a conditional node.Example: refinement of ports due to non-deterministic choice.Example: array refinement does not imply every individual port refinement.Using weights for ordering data-flow edgesUsing weights to determine <i>join</i> behavior.Weight when the condition on a conditional node is false. |

| 5.7 | Order preserved by refinement and optimization                                                                              | 51 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 5.8 | Order preserved by refinement and exclusive data-flow edge                                                                  | 52 |

| 5.9 | Graph refinement: property expressing relation between outputs and in-<br>puts of graphs independent of underlying behavior | 54 |

| 6.1 | Common subexpression elimination.                                                                                           | 56 |

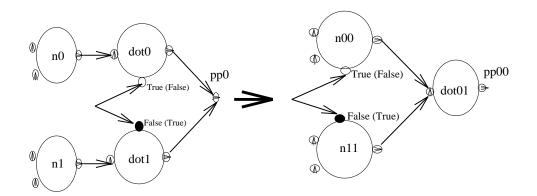

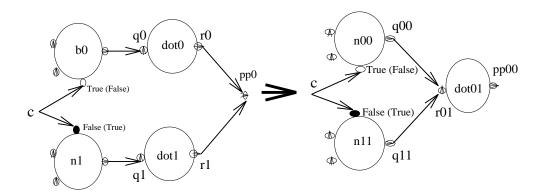

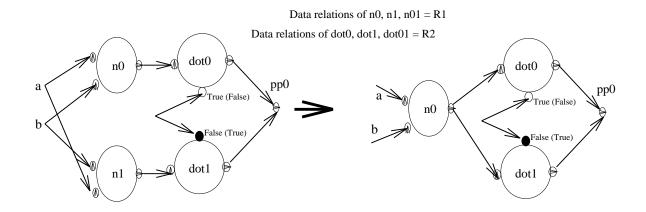

| 6.2 | Cross-jumping tail-merging: corrected                                                                                       | 58 |

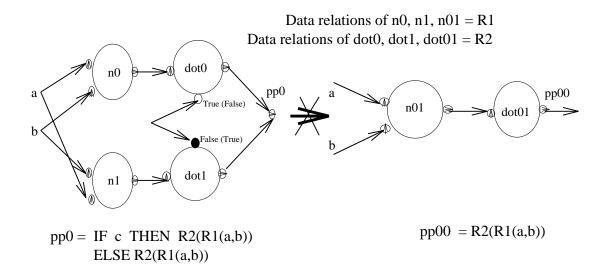

| 6.3 | Cross-jumping tail-merging: incorrectly specified in informal document.                                                     | 59 |

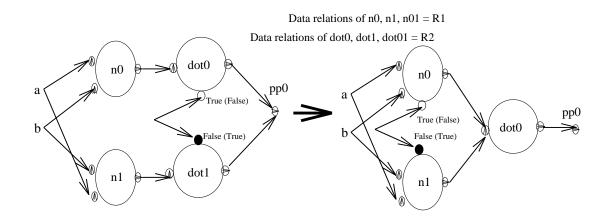

| 6.4 | Cross-jumping tail-merging: generalized and verified                                                                        | 60 |

| 6.5 | Cross-jumping tail-merging: inapplicable when two nodes are merged into one                                                 | 62 |

| 6.6 | Further optimization impossible using existing transformations                                                              | 63 |

| 6.7 | Inapplicability of cross-jumping tail-merging after common subexpression elimination: due to precondition restrictions.     | 63 |

| 6.8 | Inapplicability of common subexpression elimination after cross-jumping tail-merging: due to precondition restrictions      | 64 |

| 6.9 | A simple new transformation: obvious, post-facto.                                                                           | 65 |

# List of Tables

| 4.1  | PVS types for data-flow edge and sequence edge                                                                              | 34 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | $\rm PVS$ specification of conditional node as a record type $\ . \ . \ . \ . \ .$                                          | 36 |

| 4.3  | Node as a subtype of a conditional node                                                                                     | 38 |

| 5.1  | Using weights for ordering data-flow edges: PVS specification                                                               | 46 |

| 5.2  | Using weights to determine $join$ behavior                                                                                  | 47 |

| 5.3  | Weight when the condition on a conditional node is false                                                                    | 48 |

| 5.4  | Absence of join: exclusive data-flow edge                                                                                   | 49 |

| 5.5  | Array version of exclusive data-flow edge                                                                                   | 49 |

| 5.6  | A theorem on join of exactly two data-flow edges $\ldots \ldots \ldots \ldots \ldots$                                       | 50 |

| 5.7  | Order preserved by refinement and optimization $\ldots \ldots \ldots \ldots$                                                | 51 |

| 5.8  | Order preserved by refinement and exclusive data-flow edge $\ldots$                                                         | 51 |

| 5.9  | Graph refinement: property expressing relation between outputs and in-<br>puts of graphs independent of underlying behavior | 53 |

| 5.10 | Predicates for expressing the sameness of nodes                                                                             | 54 |

| 6.1  | Correctness of common subexpression elimination                                                                             | 58 |

| 6.2  | $\rm PVS$ specification of preconditions for cross-jumping tail-merging $\ .$                                               | 66 |

| 6.3  | Correctness of cross- jumping tail-merging                                                                                  | 67 |

| 6.4  | Number of high level inference rule applications for various transformations                                                | 67 |

# Acknowledgments

A major part of the work presented in this report was done at Philips Research Laboratories, Eindhoven, The Netherlands, from September 1993 through April 1994. I thank Ton Kostelijk for the invitation to work on the project, and for providing illuminating suggestions, support and a homelike environment. I am grateful to Corrie Huijs, Wim Kloosterhuis, Thijs Krol, Jaap Hofstede, Peter Middelhoek, and Wim Smits for their cooperation, review, and corrections. Thanks to group leader Gerard Beenker for arranging a pleasant stay in Eindhoven and providing constant support for the project, and appreciation to the group members for a lively and stimulating atmosphere. Thanks to Iskender Agi, Mark Moriconi, Peter Neumann, Sam Owre, John Rushby, and N. Shankar for comments and suggestions, and M.K. Srivas for providing in-depth corrections and remarks. Thanks to Jens Ulrik Skakkebaek of TU Denmark, Jozef Hooman and Geert Janssen of TU Eindhoven, and Paul Miner of NASA for remarks and interesting discussions related to this work. I am grateful to Jeff Joyce of UBC for the encouragement, and for suggesting applications of the work in software engineering. Thanks to Paul Gilmore for detailed observations, and to Alan Mackworth and Mabo Ito of UBC for insightful remarks.

# Chapter 1

# Introduction

Dependency graphs<sup>1</sup> are graph-based specifications of data and control flow in a system. They are used to model systems at a high level of abstraction in both hardware and software design. In high-level synthesis of hardware, a sequence of transformations is used for refinement of dependency-graph-based specifications at an abstract behavior level into dependency-graph-based implementations at the register-transfer level. Further, register-transfer-level implementations could be converted to concrete hardware designs by low-level logic synthesis. Typically, dependency graphs are represented pictorially as graph structures with an associated behavior. A transformation transforms one graph structure into another by removing or adding nodes and edges. An informal representation would lead to subtle errors, making it difficult to verify the correctness of the transformations. The problem we have addressed in this work is, how the correctness of transformations on dependency graphs can be formally specified and verified.

The behavior<sup>2</sup> of a dependency graph is the set of all tuples, where each tuple has input data values and corresponding output data values of the dependency graph. A transformation is correct if the sequence of behaviors allowed by the implementation is a subsequence of the behaviors permitted by the specification. Trivial implementations that allow an empty sequence of behaviors can be ruled out by showing either, that at least one behavior is allowed by the implementation, or that the implementation is equivalent to its specification with respect to behavior. The solution to the problem of verifying the correctness of transformations we have sought in this work, is independent of the model of behavior underlying dependency graphs.

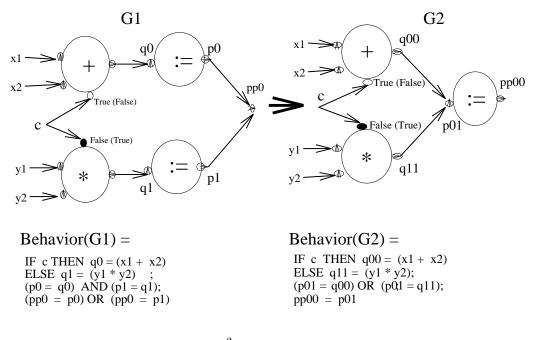

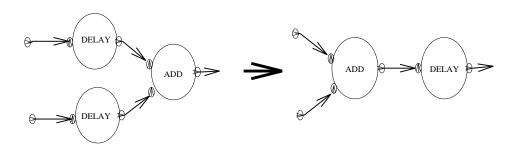

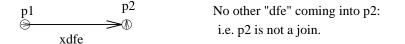

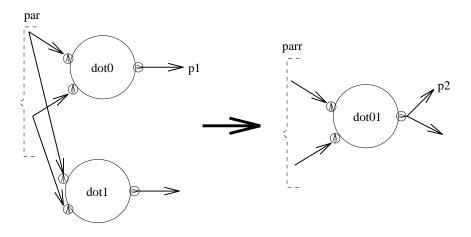

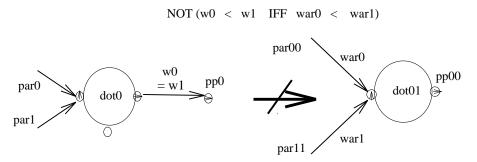

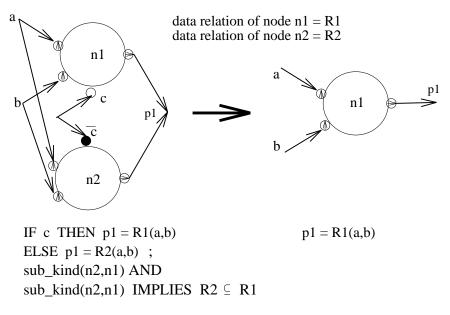

A typical transformation employed in high-level synthesis is *cross-jumping tailmerging* [EMH 93], shown in Figure 1.1. In this transformation, two identical nodes on dependency paths that are never active at the same time are merged into one node. However, as we found out using the formal approach explained in this paper, the transformation does not preserve behavior. Informally, the reason is as follows. In graph G1,

<sup>&</sup>lt;sup>1</sup>In literature, they are also known as control-flow/data-flow graphs and signal-flow graphs.

<sup>&</sup>lt;sup>2</sup>Usually known as input/output behavior.

Behavior(G1)  $\stackrel{?}{=}$  Behavior(G2)

Figure 1.1: Cross jumping tail merging: incorrectly specified in informal document.

when c is false, the value of q0 is arbitrary, and so is the value of p0. If we choose the value of pp0 to be that of p0, the value of pp0 is also arbitrary. In graph G2, when c is false, we could choose the value of p01 to be that of q11. In this case, the value of pp00 is (y1 \* y2). Because the corresponding outputs could be unequal with identical inputs, the behaviors of the graphs are not equivalent. A corrected and generalized cross-jumping tail-merging transformation is presented in Chapter 6.

The main contributions of this work are the following:

- A formal specification of dependency graphs has been achieved.

- A set of optimization and refinement transformations on dependency graphs used in high level synthesis have been verified. Generalization of transformations have also been proposed.

- Errors have been discovered in the transformations used in industrial strength hardware design. Modifications for the erroneous transformations have been proposed and incorporated.

- New transformations have been devised that could be used for further optimization and refinement than were possible before.

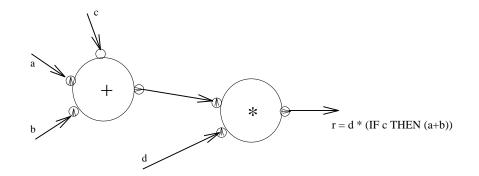

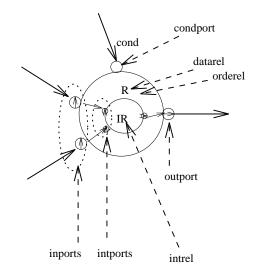

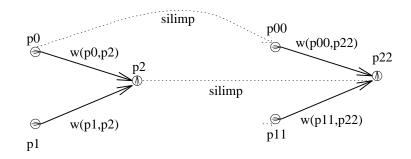

Figure 1.2: Example of a dependency graph with control specification.

Formal methods could be divided into two main categories: property-oriented methods and model-oriented methods [JMW 90]. In a property oriented method, the system under consideration is specified by asserting properties of the system, minimizing the details of how the system is constructed. While, in a model-oriented method, the specification describes the construction of the system from its components. An axiomatic approach is a property-oriented method. Typically, a small set of properties, called *axioms*, are asserted to be true, while other properties, called *theorems*, are derived. In this work, we have chosen a property oriented method. We propose an axiomatic specification coupled with an efficient verification method to study the correctness of transformations on dependency graphs. As we discuss later in Chapter 7, an axiomatic approach does not require us to develop a concrete behavioral model for dependency graphs, thus enabling it to be simpler and more general than other formal approaches.

Dependency graph<sup>3</sup> is a graph-based representation of the behavior of a system. It consists of nodes representing operations or processes, and directed edges representing data dependencies and data flow through the system. In addition, control flow could also be represented in a dependency graph in several ways. We show an example of such a graph in Figure 1.2.

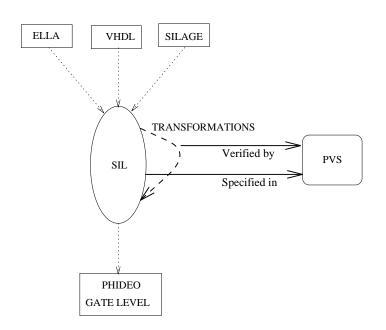

In order to present our work in a concrete context, we consider a transformational design approach used in the *high-level behavioral synthesis* system as part of the SPRITE project at Philips Research Labs (PRL). In this approach, transformations are used for optimization and refinement of descriptions specified using the SPRITE Input Language (SIL). Descriptions in SIL at a *register-transfer level* could eventually be converted to gate-level hardware designs by a *logic synthesis* application such as PHIDEO at PRL.

SIL is an intermediate language used during the synthesis of hardware described using hardware description languages such as VHDL [VHD 88], SILAGE [Hil 85], and ELLA [ELL 90]. It also forms the backbone of the TRADES synthesis system at the University of Twente. Important features of SIL include hierarchy and design freedom. Design freedom is provided by permitting several implementation choices for a

$<sup>^{3}</sup>$ In this report, the term dependency graph includes control-flow/data-flow graphs and signal-flow graphs.

SIL description. Implementation choices are constrained by allowing an implementation suggestion in a SIL description. The implementation suggestion may be tailored by using refinement and optimization transformations. SIL has been used in the design of hardware for audio and video signal processing applications such as a direction detector for the progressive scan conversion algorithm [WMM 94, Mid 94-2]. In one of the applications [Mid 94], a reduction of power consumption by 50% has been achieved.

Many of the optimization transformations used in SIL are inspired by those used in compiler optimization, such as dead-code elimination and common subexpression elimination. An optimized SIL graph has to satisfy the original graph with respect to behavior. This satisfaction can be guaranteed by showing the correctness of the optimization transformations. Correctness means that every behavior allowed by an optimized SIL graph implementation is required to be one of the behaviors allowed by its SIL graph specification. An informal specification of SIL has been presented and documented as part of the SPRITE project [Klo 92, Kro 92]. A detailed denotational semantics of SIL for showing the correctness of transformations has been worked out earlier [HHK 92, HuK 94]. The optimization and refinement transformations have been specified informally as part of the SPRITE project [EMH 93, Mid 93, Mid 94].

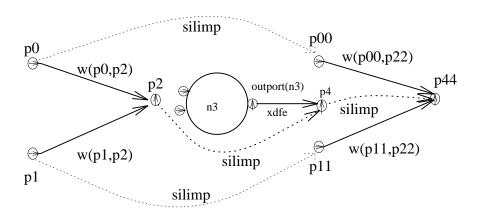

We use the Prototype Verification System (PVS) [OSR 93], an environment for formal specification and verification. The PVS specification language, based on typed higher-order logic, permits an axiomatic method to develop specifications. This method entails expressing properties of a system at a convenient level of abstraction. The choice of a high level of abstraction obviates the need to provide a detailed definition of the behavior of dependency graphs. For example, a behavior model could be based on behavior expressions [McP 83], an imperative semantics [Cam 89], a denotational model [GGJ 93,HuK 94], or an operational model [GGJ 93]. In the axiomatic framework we discuss in this report, we can compare descriptions with respect to their behavior, and thus establish correctness of transformations, without specifying a behavioral model of a SIL description. However, we stress that this work addresses the transformations as intended in their informal specification, and not verification of the software implementations of transformations. We show SIL and our work in the context of the synthesis system in Figure 1.3.

The rest of this report is organized as follows: Chapter 2 gives an overview of SIL. In Chapter 3, we give a brief description of the PVS system. In Chapter 4, we describe the specification of structure of SIL graphs, while in Chapter 5 we describe the specification of behavior, refinement, and equivalence of SIL graphs. We present the specification and verification of transformations in Chapter 6. In that chapter, we also illustrate how our generalization and composition of transformations leads to new transformations for further optimization and refinement than would have been possible before. Finally, following a general discussion, conclusions are summarized in Chapter 7. A listing of the specification of SIL and its verified properties as it appears in PVS is given in Appendix A. Transcripts of the verification in PVS for two transformations discussed

Figure 1.3: SIL transformations and verification in PVS in the context of high level synthesis.

in detail in this paper are listed in Appendix B. In the remainder of this chapter, we discuss related work done in the past.

## 1.1 Related Work

There have been some efforts in analysis and verification of refinement transformations in the past. However, few have dealt with transformations on dependency graphs in general. Most of the efforts have concentrated on specialized hardware description languages and programming languages.

A formal model was proposed for verifying correctness of high-level transformations by McFarland and Parker [McP 83]. Transformations used in YIF (Yorktown Internal Form) [YIF 88] have been proved to be behavior preserving [Cam 89]. In this work, a strong notion of behavior equivalence based on an imperative semantics tied to a particular model of representation is used. A formal system using transformations for hardware synthesis has been discussed by Fourman [Fou 90]. We briefly discuss this work in Section 1.1.1. A synthesis system for a language based on an algebraic formalism has been presented by Jones and Sheeran [Jon 90], and its formalization has been presented by Rossen [Ros 90]. This effort is explained briefly in Section 1.1.2. Another algebraic approach to transformational design of hardware has been worked out by Johnson [Joh 94]. A short discussion on this approach is presented in Section 1.1.3. In the work on tying formal verification to silicon compilation [JRS 91], a preliminary study with an emphasis on the use of formal verification at higher levels of VLSI design was presented. Correctness of register-transfer-level transformations for scheduling and allocation has been dealt with in [Vem 90].

An automatic method for functional verification of retiming, pipelining and buffering optimization has been presented by Kostelijk [KoW 93]. It has been implemented in a CAD tool called RetLab as part of PHIDEO at PRL. A formal analysis of transformations used in Systems Architect Workbench (SAW) high-level synthesis was studied by McFarland [McF 93]. This work is discussed briefly in Section 1.1.4. A post-facto verification method for comparing logic level designs against a restricted class of data-flow graphs in SILAGE was presented by Aelten and others [AAD 93, Ael 94]. Denotational and operational models of generalized data-flow graphs have been developed, but they have not been used to study the correctness of transformations [GGJ 93]. A formalization of SILAGE transformations in HOL was studied by Angelo [Ang 94]. A concise description of this work appears in Section 1.1.5. An approach based on the execution model for representation languages in BEDROC high-level synthesis system [CBL 92] has been used to verify the correctness of optimization transformations. A formal verification of an implementation of a logic synthesis system has been reported by Aagard and Leeser [AaL 94], but it does not provide a mechanical verification for transformations in high-level synthesis. A brief discussion of the work on verification of transformations in synchronized transitions [Sta 90] is given in Section 1.1.6. In Section 1.1.7, we briefly discuss the work on formal specification and verification of refinement transformation in software design.

#### 1.1.1 LAMBDA

LAMBDA [Fou 90] is formal system based on higher order logic for designing hardware from high level specifications. In this formalism, a design state is represented as an inference rule derived within the framework of higher order logic. A refinement is a rule derived within this logic that can be applied to an abstract design state to arrive at a concrete design state. The different kinds of refinements that are applied are temporal, data and behavioral. However, a definite set of refinement and optimization transformations have not been presented. ELLA, a hardware description language has been formalized in LAMBDA.

#### 1.1.2 Formal Ruby

In this work, an algorithmic specification of sequential and combinational circuits is specified in a language called Ruby [Jon 90], based on an algebraic formalism. The algebraic formalism consists of relations and operations on relations such as composition, inverse and conjugation. Types are defined as equivalence relations. Data structures such as lists and tuples are used to represent larger hardware structures. A parallel composition operator allows to specify hardware composed of independent modules. Other operators such as row and column are introduced for succinct specification of regular structures such as systolic arrays.

Ruby has been formalized [Ros 90] in a proof checking system called ISABELLE. ISABELLE, based on type theory, allows syntactic embedding other logics. A fragment of Ruby corresponding to combinational circuits, delay element, serial composition and parallel composition called Pure Ruby is specified as a type. Properties and proof rules such as induction on Ruby terms is then derived on the type definition. The rest of the language is then specified using this type.

The axiomatization specifies signals as functions of time and properties of relations on signals. General properties of Ruby relations have been formalized. However, in order to derive properties, the semantic embedding involves signals corresponding to a circuit implementation. A Ruby specification itself, and hence its formalization even at a high level is geared to be directly translatable to a circuit realization having a regular structure. Thus, this formalism is at a lower level of abstraction than our formalization of SIL. A general concept of refinement is not formalized. The formalism does not present a well-defined set of transformations, to be used to refine and optimize Ruby programs, other than retiming.

#### 1.1.3 Digital Design Derivation

This is an algebraic approach to transformational design of hardware [Joh 94]. In this formalism, a functional specification is translated into a representation of a Deterministic Finite State Machine specification called behavior tables [RTJ 93]. The behavior tables are transformed into a digital design. In a behavior table, rows represent state transitions and columns represent both control and data flow. Some examples of transformations are column merging, deletion and renaming. The transformations are not formally verified.

#### 1.1.4 Transformations in SAW

In this work, a formal analysis of transformations [McF 93] used in System Architect's Workbench (SAW) [Tho 98] is carried out. In this system, hardware described at the register-transfer level or higher using ISPB [Bar 81] is translated into behavior expressions. Behavior expressions use sequences and relations on sequences to represent the input/output behavior of the specified hardware. Optimization transformations are carried out on the behavior expressions representations. A number of transformations such as constant folding and loop unwinding have been analyzed revealing a few conceptual errors.

#### 1.1.5 Verification of Transformations in SILAGE

SILAGE [Hil 85] is an applicative hardware description language. This language is used to describe hardware represented as data-flow graphs. Transformations such as commutativity and retiming are used to optimize and refine SILAGE descriptions. In this work [Ang 94], the syntax and semantics of SILAGE programs have been formalized as predicates in HOL [GoM 93]. The denotational semantics of SILAGE have been formalized in HOL. The equivalence of SILAGE programs is specified with respect to this denotational semantics. The transformations are then specified as functions from one formal SILAGE program to another. The correctness of transformations are thus verified with respect to the denotational semantic notion of equivalence.

#### 1.1.6 Synchronized Transitions in LP

Synchronization Transitions (ST) [Sta 90] is a formalism to specify states and transitions between states. It is based on UNITY [UNI 88] model of computation as a collection of atomic conditional assignments to state variables without explicit flow of control. The transitions are specified by guarded commands. State variables model storage and sharing of state variables model communication. This is unlike message passing in CSP [Hoa 85] formalism and token passing in SIL. There is no concept of clocks and sequencing. The temporal behavior is determined by guards. The formalism is geared towards direct realizations in synchronous and asynchronous circuits. The optimization and refinement transformations are not defined in the language. The conditions to be satisfied by an abstraction function, mapping a concrete state set to an abstract state set have been presented.

The specification that an ST program has to satisfy can be described as an invariant. An ST program could then be directly translated into Larch Prover (LP) [GaG 89], and invariants translated as proof obligations to be discharged. LP is a rewrite rule prover based on first order equational logic. Thus, an ST program can be both directly translated to LP and verified, and realized in hardware through synthesis.

#### 1.1.7 Transformations in Software Design

There have been several efforts in specification and verification of refinements used in program development from high level specifications Most of the efforts choose a specification formalism and develop a notion of correctness, and an associated set of transformations based on the semantics of the formalism.

The refinement calculus [Bac 88] for specifications based on Dijkstra's guarded command language and weakest precondition semantics has been formalized in HOL [WrS 91]. Transformations such as data refinement and superposition have been verified to be correct. A formalization of incremental development of programs from specifications for distributed real-time systems has been worked out in PVS [Hoo 94]. In this formalism, an assertional method based on a compositional framework of classical Hoare triples is developed for step-wise refinement of specifications into programs.

The KIDS [Kid 90] system is a program derivation system. High level specifications written in a language called Refine are transformed by data type refinements and optimization transformations such as partial evaluation, finite differencing, into a Refine program.

## Chapter 2

# **Overview of SIL**

The descriptions in SIL are characterized as graphs. They are used to describe synchronous systems. A denotational semantics of SIL has been worked out by Huijs [HuK 94]. The behavior of a SIL graph is derived from the behaviors of structural building blocks of the graph. We briefly explain the structural aspects in section 2.1, the behavioral aspects in Section 2.2, and the transformational approach in Section 2.3

### 2.1 Structural Aspects of SIL

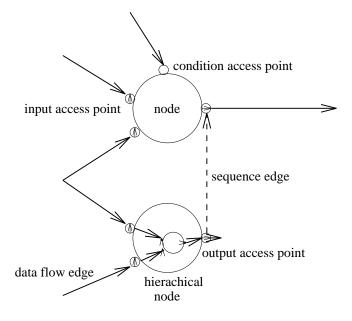

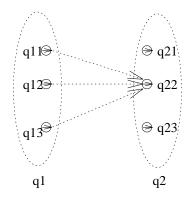

The basic building blocks of a SIL graph are the nodes for operations such as addition, multiplication, and multiplexing. The nodes have ports (also known as access points) for input, output, and an optional condition input. Every port is associated with a type, which specifies the set of data values that the port can hold. We show the different kinds of port in Figure 2.1.

While input and output ports can be of any type, a condition input port is always Boolean. A node with condition input port is known as a conditional node to stress the presence of the condition inputs.

The ports of the nodes are connected by edges. SIL has different kinds of edges, of which, we address *sequence edge* and *data-flow edge*:

© Input Access point Non-inverted Condition Access point ⊖ Output Access point Inverted Condition Access point Figure 2.1: Different kinds of SIL ports.

Figure 2.2: An example of a SIL graph description.

- A *data-flow edge* is used to specify the direction of communication of data values from a *source* port to a *sink* port. Each data-flow edge has exactly one port at its head and exactly one port at its tail. A source port can be the tail of more than one data-flow edge, in which case it is called a distribute, and a sink port the head of more than edge, in which case it is called a join.

- A sequence edge specifies an ordering between two ports. The ordering is used to indicate that one of the ports has the overriding influence on the value of the sink port, to which the two ports are connected by data-flow edges. Each sequence edge has exactly one port as its tail and one port as its head. Sequence edges are primarily used to resolve potential conflicts at joins. All source ports that are tails of data-flow edges with a join as a head must be linearly ordered by sequence edges.

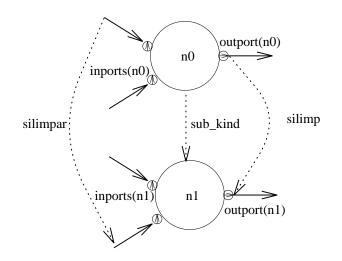

- The nodes and edges form a SIL graph. A SIL graph itself can be viewed as one single node, and used to construct another SIL graph in a hierarchical manner. Figure 2.2 is an example of a SIL graph.

### 2.2 Behavioral Aspects of SIL

The behavior of a SIL graph is determined by the behavior of individual nodes and their connectivity, which determines the data flow. By behavior, we mean the set of

Figure 2.3: SIL node: informal description.

tuples, where each tuple has input data values and corresponding data values of internal and output ports. The values of internal and output ports are constrained by the data relations of the nodes and the connectivity of the ports in the graph. When the ports of interest are the outermost input / output (I/O) ports of the SIL graph, then it is called external or I/O behavior.

Each node is associated with a data relation and an order relation. The data relation of a node constrains the outputs of the node according to the inputs of the node. That this is a *relation*, and not a *function*, implies nondeterminism allowing several implementation choices for the nodes. This contributes to design freedom. Any state information implicit in the node is incorporated into its data relation. In the case of a conditional node, the output is constrained by the data relation only when the condition input of the node is true. When the condition input is false, the output is not defined. The order relation specifies constraints such as, the output port of a node assumes a value after the value of its input ports have been asserted. This is particularly important in a hierarchically built node. We illustrate these concepts in Figure 2.3.

The communication of data values in a SIL graph is modeled by a single token flow concept, similar to the concept in Signal FLow Graphs (SFG) [Hil 85]. A token is an atomic symbol denoting data. A token generated at an output port (source) is transmitted through a data-flow edge, emanating from the source, exactly once. The token is consumed at an input port (sink) to which the edge is connected. The action of communicating a token through a data-flow edge makes the sequence of values that the sink can assume equal to the sequence of values that the source can assume. However, there is one exception to this when a token communicated to the conditional port of a conditional node denotes a data value that is *false*. In this case, the output port, unconstrained by the data relation of the conditional node, is not defined. When such an output is a source of a data-flow edge, we force the sink of such a data-flow edge to assume some well-defined arbitrary value. If we do not make this exception, the sink data values would also not be well-defined. Since a sink is an input port, it is undesirable to have undefined inputs in practice. In terms of the token flow concept, a sequence edge from port A to port B describes that the token fired from B determines the value of a sink port C connected to A and B by data-flow edges, overriding the effect on the value of C due to the token fired from A. In such a case, we say that the sequence edge orders port A less than port B. A data-flow edge has an implicit sequence edge from its source to its sink. We depict these ideas in Figure 2.4. It should be noted that the token flow concept is an abstract model of the behavior of a SIL graph. The sequence edge is an artifact used to resolve conflicts at joins. A sequence edge does not indicate temporal ordering of the data values that ports would assume when a SIL graph is executed.

The ordering of token communication plays an important part in resolving conflicts at ports. One such conflict occurs when multiple data-flow edges from different sources connect into a single sink. Such a sink port is called a *join*, as shown in Figure 2.5. To resolve the conflict at a join, first all the data-flow edges that have sources that can assume well-defined data values are selected. Then, among those selected data-flow edges, the edge that is responsible for communicating the last token determines the behavior of the join. With the definition of SIL, there will be exactly one such data-flow edge. Thus, the source ports are linearly ordered, so that the last of the well-defined data values arriving at the sink is always specified. If all the data-flow edges to the join originate from sources whose data values are undefined, then the data value that can appear at the join is arbitrary.

The counterpart of a join is a source from which multiple data-flow edges originate. Such an port, known as a *distribute*, is shown in Figure 2.5. If a distribute is a source that assumes well-defined data values, then the sink to which it is connected by a data-flow edge, will assume a sequence of data values identical to the distribute. Otherwise, if the data values that may appear at the distribute are not defined, the sequence of data values that may appear at the corresponding sink ports are arbitrary.

A SIL graph models the behavior of a system during a single clock cycle. There is no explicit notion of state in a SIL graph. The repetition of a SIL graph, called *unfold*ing over multiple clock cycles gives the behavior of the system across clock cycles. We depict an example of a combinational adder in Figure 2.6 unfolded over three clock cycles. The DELAY node, one of the primitive nodes in SIL is used to model data flow between clock cycles, and thus encapsulates state information. We can unfold the SIL graph shown in Figure 2.7 over multiple clock cycles to result in a SIL graph without the DELAY node. The *cumulative* adder example in Figure 2.8 illustrates the unfolding of a SIL graph with a DELAY node. It should be noted that comparing two graphs with respect to behavior would not involve the state information encapsulated in a DELAY node - since the behavior of a SIL graph would be a snapshot of the execution of the SIL graph in a single clock cycle. In contrast, the execution histories would have to be taken into account for comparing two state machine models.

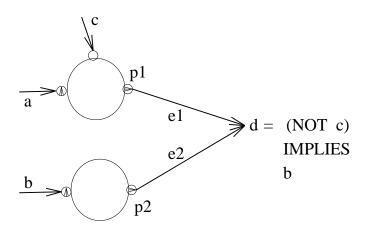

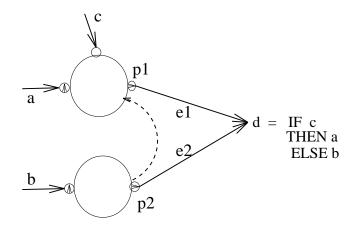

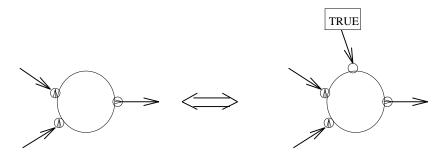

The ordering imposed by sequence edges reduce non-determinism This leads to a restriction on implementation choices allowed by its corresponding specification. We illustrate the implementation of a simple multiplexor in Figure 2.10 by reducing non-determinism in a specification shown in Figure 2.9 using a sequence edge. When c is

Figure 2.4: SIL edges: informal description.

Figure 2.5: SIL Join and Distribute: informal description.

Figure 2.6: Combinational adder: SIL graph repeated over clock cycles.

Figure 2.7: Cumulative adder: SIL graph with DELAY node.

c(-1) = 0c(t) = a(t) + c(t-1)

Figure 2.8: Cumulative adder: unfolded SIL graph.

Figure 2.9: Partial specification of a multiplexor.

Sequence edge from p2 to p1 means that, the token at p1 overrides the token from p2 in determining the value at d

Figure 2.10: Implementation specification of a multiplexor.

true, the value of d is a if the order is such that value of port p1 is communicated rather than that of port p2. If the order is such that p2 has the overriding influence, then the value of d is b. While, when c is *false* the value of b is determined by the port p2, due to the behavior of the conditional port and join discussed earlier in section 2.2. The sequence edge in the multiplexor implementation as given in Figure 2.10, imposes that the value communicated to b is that of port p1 when c is *true*. Again, when c is *false*, port p2 determines the value of b.

### 2.3 Transformations in SIL

A transformation is viewed as modifying the structure of a graph into another graph. The modification is done by removing and/or adding nodes and edges. Such modifications should not violate the behavior of the original graph.

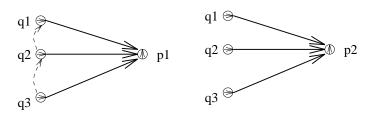

In SIL, there are a number of optimization and refinement transformations [EMH 93]. Many of the optimization transformations are inspired by compiler optimization techniques such as *Common Subexpression Elimination*, *Cross-Jumping Tail-Merging* and algebraic transformations involving *commutativity*, associativity, and distributivity. Other optimization transformations include *retiming*. Refinement transformations include type transformations such as *real to integer*, *integer to Boolean*, and implementing data relations of the nodes by concrete operators [Mid 94]. We show a retiming transformation example in Figure 2.11

Figure 2.11: Example SIL transformation: retiming.

## Chapter 3

# Specification and Verification in PVS

The Prototype Verification System (PVS) [OSR 93, SOR 93-2] is an environment for specifying entities such as hardware/software models and algorithms, and verifying properties associated with the entities. An entity is usually specified by asserting a small number of general properties that are known to be true. These known properties are then used to derive other desired properties. The process of verification involves checking relationships that are supposed to hold among entities. The checking is done by comparing the specified properties of the entities. For example, one can compare if a register-transfer-level implementation of hardware satisfies the properties expressed by its high-level specification.

PVS has been used for reasoning in many domains, such as in hardware verification [Cyr 93, CRS 94], protocol verification, and algorithm verification [LOR 93]. We briefly give the features of the PVS specification language in Section 3.1, the PVS verification features in Section 3.2 and some notes on the syntax of the PVS specification language in Section 3.3. Finally, in Section 3.4 we give some example specifications and verification sessions in PVS.

## 3.1 PVS Specification Language

The specification language [OSR 93] features common programming language constructs such as arrays, functions, and records. It has built-in types for reals, integers, naturals, and lists. A type is interpreted as a set of values. One can introduce new types by explicitly defining the set of values, or indicating the set of values, by providing properties that have to be satisfied by the values. The language also allows hierarchical structuring of specifications. Besides other features, it permits overloading of operators, as in some programming languages and hardware description languages such as VHDL.

## 3.2 PVS Verification Features

The PVS verifier [SOR 93-2] is used to determine if the desired properties hold in the specification of the model. The user interacts with the verifier by a small set of commands. The verifier contains procedures for boolean reasoning, arithmetic and (conditional) rewriting. In particular, Binary Decision Diagram (BDD) [BRB 90, Jan 93] based simplification may be invoked for Boolean reasoning. It also features a variety of general induction schemes to tackle large-scale verification. Moreover, different verification schemes can be combined into general-purpose strategies for similar classes of problems, such as verification of microprocessors [Cyr 93, CRS 94].

A PVS specification is first parsed and type-checked. At this stage, the type of every term in the specification is unambiguously known. The verification is done in the following style: we start with the property to be checked and repeatedly apply rules on the property. Every such rule application is meant to obtain another property that is simpler to check. The property holds if such a series of applications of rules eventually leads to a property that is already known to hold. Examples illustrating the specification and verification in PVS are described in Section 3.4.

## 3.3 Notes on Specification Notation

In PVS specifications<sup>1</sup>, an object followed by a colon and a type indicates that the object is a constant belonging to that type. If the colon is followed by the key word VAR and a type, then the object is a variable belonging to that type. For example,

```

x: integer

y: VAR integer

```

describes x as a constant of type integer, and y as a variable of type integer<sup>2</sup>.

Sets are denoted by {...}: they can be introduced by explicitly defining the elements of the set, or implicitly by a characteristic function. For example,

{0,1,2}

{x: integer | even(x) AND x /= 2}

<sup>&</sup>lt;sup>1</sup>PVS specifications in this report are enclosed in framed boxes.

<sup>&</sup>lt;sup>2</sup>In C, they would be declared as *const int x; int y*.

The symbol | has to be read as *such that*, and the symbol /= stands for *not equal to* in general. Thus, the latter example above should be read as "set of all integers x, such that x is an even number and x is not equal to 2".

New types are introduced by a key word TYPE followed by its description as a set of values. If the key word TYPE is not followed by any description, then it is taken as an unspecified type.

Some illustrations are:

```

even_time: TYPE = {x: natural| even(x)}

unspecified_type: TYPE

```

One kind of type that is used widely in this work is the *record type*. A record type is like the *struct* type in the C programming language. It is used to package objects of different types in one type. We can then treat an object of such a type as one single object externally, but with an internal structure corresponding to the various fields in the record.

The following operators have their corresponding meanings:

FORALL x: p(x)

means for every x, predicate<sup>3</sup> p(x) is true

EXISTS x: p(x)

means for at least a single x, predicate p(x) is true

We can impose constraints on the set of values for variables inside FORALL and EXISTS as in the following example:

FORALL x, (y | y = 3\*x): p(x,y)

which should be read as

for every x and y such that y is 3 times x, p(x,y) is true.

A property that is already known to hold without checking is labeled by a name followed by a colon and the keyword AXIOM. A property that is checked using the rules available in the verifier is labeled by a name followed by a colon and the keyword THEOREM. The text followed by a % in any line is a comment in PVS. We illustrate the syntax as follows:

<sup>&</sup>lt;sup>3</sup>A predicate is a function returning a Boolean type:  $\{true, false\}$ .

```

ax1: AXIOM % This is a simple axiom

FORALL (x:nat): even(x) = x divisible_by 2

th1: THEOREM % This is a simple theorem

FORALL (x:nat): prime(x) AND x /= 2 IMPLIES NOT even(x)

```

We also use the terms *axiom* and *theorem* in our own explanation with the same meanings. A *proof* is a sequence of steps that leads to a *theorem*.

### 3.4 Specification and Verification Examples in PVS

We illustrate here three examples from arithmetic. The first two examples are taken from the tutorial [SOR 93-1]. The last example illustrates the use of a general purpose strategy to automatically prove a theorem of arithmetic. The first example is the sum of natural numbers up to some arbitrary finite number n is equal to  $n^*(n+1)/2$ . The specification is encapsulated in the sum THEORY. Following introduction of n as a natural number nat, sum(n) is defined as a recursive function with a termination MEASURE as an identity function on n. Finally, the THEOREM labeled closed\_form is stated to be proved.

```

sum: THEORY

BEGIN

n: VAR nat

sum(n): RECURSIVE nat =

(IF n = 0 THEN 0 ELSE n + sum(n - 1) ENDIF)

MEASURE (LAMBDA n: n)

closed_form: THEOREM sum(n) = (n * (n + 1))/2

END sum

```

The THEORY is first parsed and type checked, and then the prover is invoked on the closed\_form THEOREM. The proof is automatic by applying induction and rewriting. The proof session is as follows:

closed\_form :

|-----{1} (FORALL (n: nat): (sum(n) = (n \* (n + 1)) / 2))

```

Running step: (INDUCT "n")

Inducting on n,

this yields 2 subgoals:

closed_form.1 :

|-----

\{1\} sum(0) = (0 * (0 + 1)) / 2

Running step: (EXPAND "sum")

Expanding the definition of sum,

this simplifies to:

closed_form.1 :

|-----

\{1\} 0 = 0 / 2

Rerunning step: (ASSERT)

Invoking decision procedures,

This completes the proof of closed_form.1.

closed_form.2 :

|-----

\{1\}

(FORALL (j: nat):

(sum(j) = (j * (j + 1)) / 2)

IMPLIES sum(j + 1) = ((j + 1) * (j + 1 + 1)) / 2))

Running step: (SKOLEM 1 ("j!1"))

For the top quantifier in 1, we introduce Skolem constants: (j!1),

this simplifies to:

closed_form.2 :

|-----

{1} sum(j!1) = (j!1 * (j!1 + 1)) / 2

IMPLIES sum((j!1 + 1)) = ((j!1 + 1) * ((j!1 + 1) + 1)) / 2

Running step: (FLATTEN)

Applying disjunctive simplification to flatten sequent,

this simplifies to:

closed_form.2 :

```

```

{-1}

sum(j!1) = (j!1 * (j!1 + 1)) / 2

|----

sum((j!1 + 1)) = ((j!1 + 1) * ((j!1 + 1) + 1)) / 2

\{1\}

Running step: (EXPAND "sum" +)

Expanding the definition of sum,

this simplifies to:

closed_form.2 :

sum(j!1) = (j!1 * (j!1 + 1)) / 2

[-1]

|-----

(j!1 + 1) + sum(j!1) = (j!1 * j!1 + 2 * j!1 + (j!1 + 2)) / 2

\{1\}

Running step: (ASSERT)

Invoking decision procedures,

This completes the proof of closed_form.2.

Q.E.D.

Run time = 8.09 secs.

Real time = 9.89 secs.

NIL

>

```